选择合适的SoC FPGA体系结构的重要性

发布时间:2014-2-26 14:14

发布者:eechina

|

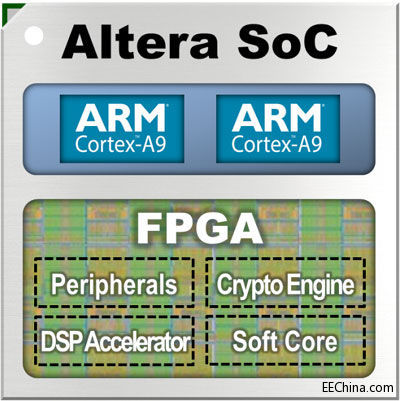

作者:Altera公司SoC产品高级市场经理Todd Koelling 在大部分嵌入式系统中,处理器和现场可编程门阵列(FPGA)完成最繁重的工作。处理器和FPGA通常单独工作,如果两种技术能够一起出色的协同工作,将形成功能更强大的嵌入式计算平台。在这些系统中,处理器一般提供高级管理功能,而FPGA完成严格的实时操作,大量的数据处理,或者处理器不太容易支持的接口功能。 SoC FPGA器件在一个器件中成功集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信,等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA的优点。 与以前的器件设计相比,SoC FPGA的功能和性能相当甚至是更好,但是减小了电路板面积,降低了功耗和系统成本——高达50%以上。通过在一个硅片上集成这些技术,系统开发人员避免了塑料封装的成本问题。如果设计中的CPU和FPGA使用分立的外部存储器,那么,设计人员应该将这些合并到一个存储器件中,进一步降低系统成本和功耗,减小电路板面积。处理器和FPGA之间的信号现在是在同一个硅片中,它们之间通信消耗的能耗要比使用分立芯片低很多。而且,处理器和FPGA之间有数千路内部连接,与两芯片解决方案相比,集成解决方案能够有效的提高带宽,降低延时。 嵌入式开发人员在为自己的应用选择最佳SoC FPGA时,需要考虑很多设计问题和工程决定。这些选择标准包括系统性能、系统可靠性、功耗、开发工具和未来发展路线图等。 采用SoC FPGA提高系统性能 最终,SoC FPGA中的系统性能是由能否在四个主要SoC功能之间高效移动数据来决定的,即,处理器、FPGA逻辑、互联,以及片内和片外存储器。 在各种应用中,系统性能主要是由数据通路性能决定的,器件应能够以“线速”处理连续数据流,很少出现失速或者中断。在这些应用中,FPGA逻辑处理关键数据通路,而处理器对控制通路进行高级管理。处理器解释一小部分到达数据,尽量不参与数据通路的工作。 为完成这种协调的合作,现代SoC FPGA采用了ARM双核Cortex-A9应用处理器,集成到高级28nm FPGA架构中。与其他应用处理器相比,Cortex-A9非常理想的同时实现了低功耗、功能、带宽和性能。 专门设计了Cyclone V SoC中的互联,FPGA逻辑和处理器之间的吞吐量高达100 Gbps以上,从而提高了系统性能,图1。FPGA逻辑和Cortex-A9处理器之间的100 Gbps互联保证了系统有足够的互联性能,支持大吞吐量数据流。

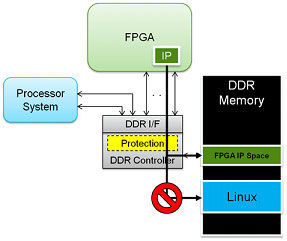

图1.Cyclone V SoC,FPGA和处理器之间>100 Gbps互联 能够有效的访问片内和片外存储器也使得SoC FPGA提高了系统性能。Cyclone V SoC中的硬核存储器控制器采用了复杂算法,尽可能提高您存储器的效率。这些算法使用缺陷权重罗宾带等复杂算法,管理会话优先级、对命令和数据重新排序、调度未完成的会话,从而提高了存储器带宽。其他的性能源自通过软件定制存储器控制器,与定制数据指标非常符合。 评估存储器控制器性能时,重要的是不仅仅要关注总线宽度和速度。LMbench等系统级基准测试适用于查看存储器子系统的总体性能。在667MHz Cyclone V SoC系统上运行LMbench基准测试表明,具有智能存储器控制器的Cyclone V SoC的存储器带宽更高——比竞争SoC器件高出17%,而且存储器工作频率降低了25%。这种在效率上的优势支持Cyclone V SoC以更低的时钟速率实现更大的带宽,降低了系统功耗。 采用SoC FPGA提高系统可靠性 随着存储器容量的不断增长,对错误探测和纠正的需求已经成为当今设计的发展趋势。大部分现代系统包括专用硬件来帮助实现数据完整性。这包括纠错码(ECC)保护——不仅仅是存储器控制器的一部分,而且还集成在处理器的片内存储器、高速缓存、外设缓冲以及FPGA中。错误检查和纠正电路使系统更可靠,系统不受意外数据错误或者数据损坏的影响。 存储器保护是通常与高级处理器中的存储器控制器相关的特性,称之为存储器管理单元(MMU)或者存储器保护单元(MPU)。处理器的存储器保护单元防止了错误或者非法的处理器会话读取甚至损坏其他存储器区。在Cortex-A9处理器中,ARM的TrustZone技术扩展了这一保护概念,为安全敏感的系统提供了系统级方法。 使用Cyclone V SoC,为操作系统和嵌入式应用软件指定了特定的存储器区域,而其他存储器区域可以专门用于基于FPGA的功能,如图2所示。通过存储器保护,FPGA主机功能不会损坏操作系统或者嵌入式软件区域。

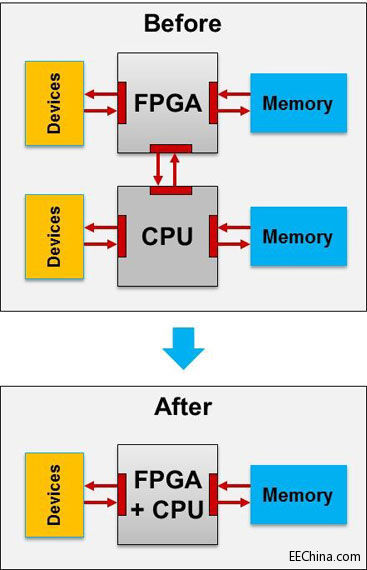

图2.SoC应用中的DDR存储器保护,处理器和FPGA共享公共的存储器。 集成降低功耗 新电子应用对功耗的要求越来越高——不仅仅是手持式设备,而且还有汽车应用,甚至是服务器机架等,这些都有很大的功耗和散热预算。SoC FPGA器件是可行的解决方案,帮助嵌入式开发人员实现其功耗预算。 如图3所示,在一片SoC FPGA中集成处理器和FPGA组件能够把系统功耗降低10%到30%。I/O在器件之间传送信号,通常需要较高的电压,是应用中最耗能的组件。

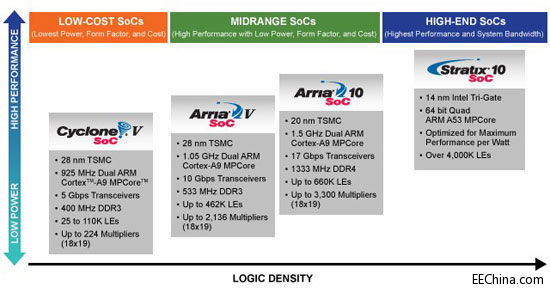

图3.在一片SoC FPGA中集成处理器和FPGA,共享外部存储器接口,减少了高功耗的芯片间I/O连接。 简单的集成不但降低了功耗,Cyclone V SoC还具有时钟选通和调整等低功耗模式。处理器和FPGA还有独立的电源平面,支持应用程序完全关断FPGA供电,而保持处理器工作,监视任何中断。 为优化功耗,SoC设计与电源设计的关系越来越密切。在系统级,电源供电设计有时候要比SoC器件本身功耗更大。这些系统的难点在于怎样在减小电源供电布局和提高供电效率之间达到均衡。有很多电源供电选择为Cyclone V SoC提供支持,高级DC-DC电源转换器技术也为其提供支持,支持设计人员满足严格的功耗预算和空间限制要求。Altera提供Enpirion电源模块新产品,非常适合满足基于SoC FPGA的嵌入式系统的空间和效率限制要求。 熟悉的开发工具支持SoC FPGA 集成了前沿ARM应用处理器和FPGA架构的新一类SoC器件,能够以更低的成本,更迅速的实现低功耗电子产品,打开了新的应用空间。但是,伴随着硬件创新,FPGA工具、片内调试、软件调试和分析工具也应该不断创新。软件最终决定了设计人员能否成功的使用这些器件。为实现更广泛的应用,软件开发人员必须找到合适的SoC FPGA,掌握其特性,就像独立处理器软件开发那样轻松高效的使用它们。 来自Altera的SoC FPGA由SoC嵌入式设计套装(EDS)提供支持,套装包括全套的ARM兼容工具包,支持在Altera SoC器件上开发嵌入式软件。它包括开发工具、实用工具程序、运行时软件,以及应用实例,帮助您迅速开始SoC嵌入式系统的固件和应用软件开发。Altera和ARM之间这种非常重要的关系导致SoC EDS提供了独特的Altera版ARM Development Studio 5 (DS-5)工具包。ARM DS-5高级多核调试功能与FPGA自适应功能相结合——能够立即看到FPGA硬件中的改动,无缝链接至Altera的SignalTap逻辑分析器,这一SoC EDS工具包帮助嵌入式软件开发人员获得了前所未有的全芯片可视化和控制能力。 当调试出现问题时,开发团队必须能够确定这是硬件还是软件问题。支持Altera SoC FPGA的工具实现了处理器子系统和FPGA子系统之间代码和波形的交叉触发,或者从波形到代码的触发,很容易找到导致这些问题的原因。结果,开发团队能够找到并跟踪系统中某一状态是怎样出现的,为什么出现。交叉触发、跟踪和全局时间戳是IP验证、定制驱动开发以及工程中系统集成部分非常重要的特性。 除了找到故障位置之外, SoC EDS还帮助嵌入式系统开发人员知道系统为什么会进入这种故障状态,是怎样进入的。ARM系统跟踪模块(STM)支持跟踪基于CPU的软件事件。当系统执行时,应用软件可以发出硬件和软件事件“探测”信号,以监视系统行为,深入探查其工作。在“FPGA自适应”调试环境中,STM支持CPU和FPGA域的事件监视,不要求系统停止工作。 未来的SoC FPGA路线图 当选择SoC FPGA时,必须确定供应商的产品路线图.如图4所示,从长期看,这将保持您的系统竞争力,支持软件前向移植。开始时,所有硅片发展路线图的基础都是硅片工艺技术。目前Altera提供的Cyclone V和Arria V SoC采用了28 nm低功耗工艺制造,帮助工业、汽车、医疗和通信等对功耗要求较高的应用降低了功耗。 Altera的下一代Arria 10 SoC优化了中端应用的性能,提高了功效,减小了外形封装,降低了成本,适合多种中端无线基础设施、广播、军事,以及计算机和存储应用。Arria 10 SoC基于TSMC的20 nm工艺技术,结合了双核Cortex-A9处理器系统和业界领先的可编程逻辑技术。实现双核Cortex-A9处理器系统简化了第一代SoC FPGA的软件移植,尺寸更小的工艺技术将性能提升至1.5 GHz。 在先进通信、军事和数据中心应用中,第三代Stratix 10 SoC将进一步突破性能和带宽。Stratix 10 SoC基于Intel 14nm三栅极工艺技术,具有64位四核ARM Cortex-A53处理器。Cortex-A53支持32位兼容模式,如果需要,很容易实现现有软件的移植。

图4.Stratix 10 SoC是Altera的第三代SoC,采用Intel的14 nm三栅极工艺技术,集成了四核Cortex-A53处理器。 SoC FPGA是功能强大的新一类可编程器件,适用于多种电子设计。最流行的商用器件集成了标准ARM双核Cortex-A9——具有丰富的外设、片内存储器、高速内部互联体系结构、分层片内存储器,还有前沿的FPGA架构。创新软件设计和调试工具支持开发人员同时查看并交叉触发芯片的两部分(处理器和FPGA)组成。市场上的这些器件表面上看起来非常相似,但实际上底层体系结构却不尽相同。 |

网友评论