ё»КүНЁ°лµәМеНЖіц¶Өәв¶ЁЦЖ»ҮSoCөөРВЙиәЖ·Ң·Ё

·ұІәК±әдӘғ2014-1-15 10:29

·ұІәХЯӘғeechina

№ШәьөКӘғ

SoCЙиәЖ

|

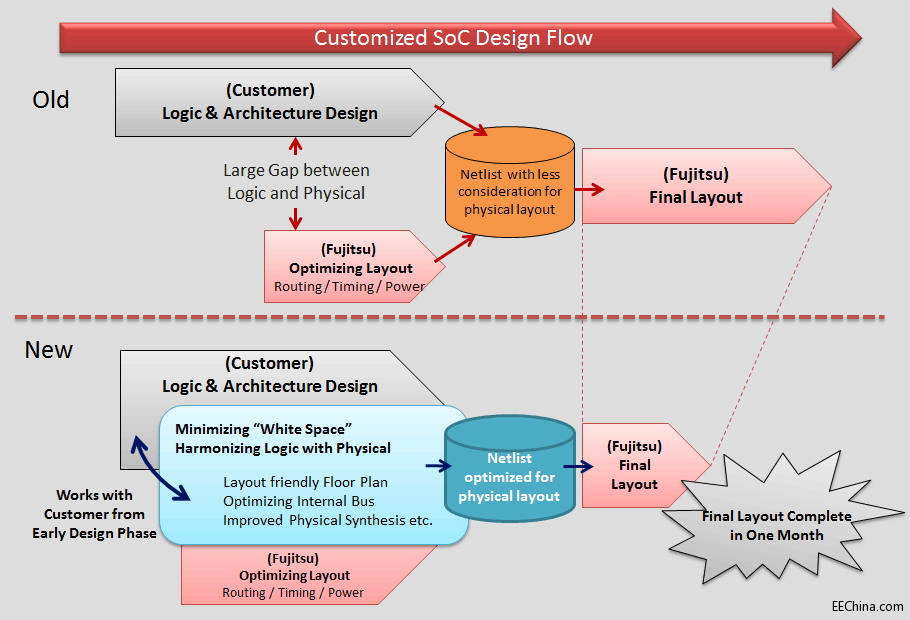

Ң«White SpaceЧоРҰ»ҮІұүЙРµчВЯәУлОпАнәЬ№№,КµПЦёьёЯµзВ·ГЬ¶ИЗТУРР§Лх¶МПЯВ·ІәңЦК±әд ё»КүНЁ°лµәМеӘЁЙПғӘӘ©УРПЮ№«ЛңҢсИХРыІәӘ¬іЙ№¦үҒ·ұБЛЧЁОҒПИҢшµД28 nm SoCЖчәюБүЙнөтФмµДИ«РВЙиәЖ·Ң·ЁӘ¬І»ҢцДЬКµПЦёьёЯµДµзВ·ГЬ¶ИӘ¬Н¬К±ТІүЙУРР§Лх¶МүҒ·ұК±әдҰӘІЙУГИ«РВЙиәЖ·Ң·ЁДЬ№»Ң«µзВ·µДГЬ¶ИМбёЯ33%Ә¬ІұүЙҢ«ЧоЦХµДПЯВ·ІәңЦК±әдЛх¶МЦБТ»ёцФВҰӘХвЦЦЙиәЖ·Ң·ЁҢ«ХығПЦБё»КүНЁ°лµәМеµДёчЦЦИ«РВ¶ЁЦЖ»ҮSoCЙиәЖ·Ң°ёЦРӘ¬РЦъүН»§үҒ·ұRTL-Handoff SoCЖчәюҰӘё»КүНЁ°лµәМеФ¤әЖЧФ2014Дк2ФВЖрҢ«үҒКәҢУКЬІЙУГХвЦЦИ«РВЙиәЖ·Ң·ЁµДSoC¶©µӨҰӘ ІЙУГ28 nmµИ¶ӨәвЦЖіМ№¤ТХµДSoCЖчәюРиТҒУРФҢАөФҢ¶аµД№¦ДЬУлР§ДЬӘ¬Ңш¶шТҒФЪРңЖ¬ЦРІәҢЁФҢАөФҢ¶аµДµзВ·ҰӘОөАөSoCµДЙиәЖҢ«ИХЗчёөФУӘ¬үҒ·ұК±әдТІҢ«»бТтөЛҢПТФНщФцәУӘ¬Н¬К±ИзғОУРР§Ңвңц№¦ғДОКМвТІіЙОҒЙиәЖХЯµДёьөуМфХҢҰӘ ОҒУ¦¶ФИХЗчёөФУµДSoCЙиәЖӘ¬ё»КүНЁ°лµәМеЛщүҒ·ұіцµДөөРВЙиәЖ·Ң·ЁДЬКµПЦёьёЯµДµзВ·ГЬ¶ИҰұёь¶МµДүҒ·ұК±іМғНҢµµН№¦ғДӘ¬ІұХығПЦБё»КүНЁ°лµәМеµДёчЦЦИ«РВ¶ЁЦЖ»ҮSoCЙиәЖ·Ң°ёЦРӘ¬РЦъүН»§үҒ·ұRTL-Handoff SoCЧйәюҰӘҢПө«НіµДЙиәЖБчіМӘ¬ЙиәЖХЯүЙІЙУГё»КүНЁ°лµәМеµДИ«РВЙиәЖ·Ң·ЁФЪПаН¬өуРҰµДРңЖ¬ЦРФцәУ33%µзВ·Ә¬¶шЗТүЙҢ«ЧоЦХµДПЯВ·ІәңЦК±әдЛх¶МЦБТ»ёцФВҰӘ И«РВЙиәЖ·Ң·ЁҢ«White SpaceУРР§ЧоРҰ»Ү И«РВµД¶АәТЙиәЖБчіМүЙ№АЛгіцҢПИЭТЧІәПЯµДЖҢГжНәӘ¬ІұёщңЭІәПЯВ·ң¶УлК±РтКХБІОҒДЪІүКэңЭЧЬПЯҢшРРУЕ»ҮҰӘХвР©ЙиәЖІҢЦиүЙҢ«ОЮ·ЁҢЁЦГң§Ме№ЬµДWhite SpaceКэБүҢµµҢЧоЙЩӘ¬Тт¶шүЙИГРңЖ¬ИЭДЙёь¶аµзВ·ҰӘ Нё№эЧЁАыәәКхРµчВЯәУлОпАнәЬ№№ өЛЧЁАыәәКхОЮРлёь¶ҮИОғОВЯәЙиәЖӘ¬әөүЙЧФ¶ҮХл¶ФОпАнІәПЯҢшРРНш±нКэңЭғПіЙӘ¬ІұүЙМбЙэХыМеЙиәЖµДІәПЯР§ВКТФә°К№К±РтКХБІ±дµГёьИЭТЧӘ¬Тт¶шүЙУРР§әхЙЩЧоЦХІәПЯБчіМЛщРиµДК±әдӘ¬ёьүЙөпµҢёьёЯµДГЬ¶ИХығП¶ИҰӘ

Нә1Әғё»КүНЁ°лµәМеИ«РВүНЦЖ»ҮSoCЙиәЖ·Ң·ЁКңТвНә ё»КүНЁ°лµәМеКЗКАҢзә¶µДASIC№©»хЙМӘ¬¶аДкАөФЛУГФЪТµҢзАЫ»эµД°БИЛіЙәЁғНЧЁң«әәКхӘ¬іЦРшМṩһХң№ғЧгµДНкХы¶ЁЦЖ»ҮSoCҢвңц·Ң°ёӘ¬ЖдЦРҢбғПБЛПИҢшЙиәЖҢЁЦГҰұЦЖФм·юОсғНПµНіә¶СРңүҰұүҒ·ұЦ§іЦµИ·юОсҰӘНё№эЙПКцҢвңц·Ң°ёӘ¬ё»КүНЁ°лµәМеҢ«ДЬЦ§іЦүН»§үмЛЩүҒ·ұёЯР§РФДЬә°КҰµзµДSoCЖчәюҰӘ үН»§БҒПµ ё»КүНЁ°лµәМеӘЁЙПғӘӘ©УРПЮ№«Лң БхкН КРіҰІү µз»°Әғ86 21-6146 3688Ә¬Kenn.Liu@cn.fujitsu.com |

НшУСЖАВЫ