ADI JESD204B FPGA调试软件加快高速设计速度

发布时间:2013-10-17 11:36

发布者:eechina

|

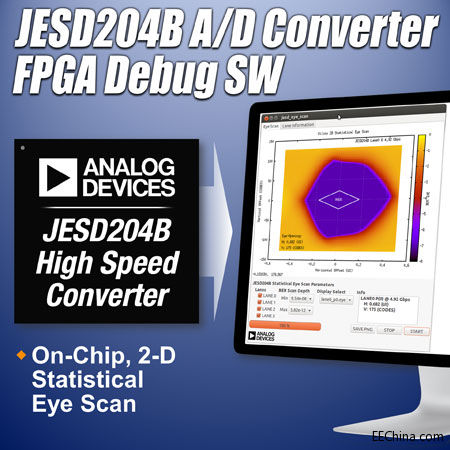

免费片内二维统计眼图扫描软件支持高速数据转换器至FPGA信号完整性的快速系统内验证 Analog Devices, Inc. (ADI)今天发布了一款基于FPGA的参考设计及配套软件和HDL代码,该参考设计可降低集成JESD204B兼容转换器的高速系统的设计风险。该软件为JESD204B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx Inc., 7系列FPGA及Zynq-7000全可编程SoC。它随ADI转换器免费提供,通过提供片内二维统计眼图扫描,帮助雷达阵列、软件定义无线电以及其他高速系统的设计人员更快地验证采用千兆收发器的JESD204B数据转换器至FPGA设计的信号完整性。

Xilinx高速I/O产品经理Revathi Narayanan表示:“ADI的JESD204B Xilinx收发器调试工具提供了片内眼图扫描功能,能以统计手段确定FPGA内部信号的完整性,是测试和测量流程的有效补充。其他技术均针对FPGA封装的外部,并在Xilinx自动增益控制和均衡器模块处理之前采集信号,而ADI则利用Xilinx收发器片内眼图扫描功能,使开发人员可以监控FPGA内部JESD204B链路上的信号完整性和设计裕量,从而获得更加准确的结果。” ADI的参考设计直接从7系列IBERT内核中的片内Rx裕量分析功能收集数据,并在FPGA或者ARM双核Cortex-A9 MPCore处理器之一的内部管理本地数据,在HDMI显示器上显示数据,或者通过以太网将数据送至远程监控站。一般地,其他扫描工具在片外测量信号,需要使用昂贵的测试和测量设备,或者需要通过JTAG传回数据,以便在实验室的主机/开发电脑上查看。 “实时”数据采集功能可监控设备健康状态 替代型扫描工具一般通过生成伪随机位流(PRBS)的方式来测量高速数据链路,而系统会在封闭开发环境中校验该伪随机位流的位级正确性。这种方式并不描述设计的实际表现,也不说明设计是否可能濒临失败。ADI的参考设计使用流向FPGA的真实JESD204B串行数据来测量链路的稳健性。通过这种利用“实时”数据的方式,即使已在现场部署设计之后,也可监控信号的保真度,从而在产品的寿命周期内进行实时、预见性维护。 报价与供货

• 下载参考设计:http://www.em.avnet.com/en-us/de ... escan-Software.aspx • 观看关于JESD204B模数转换器、FPGA和眼图扫描原理图的视频:http://videos.analog.com/video/p ... oard-with-JESD204B/ • 了解有关Xilinx FPGA的更多信息:www.xilinx.com/jesd204 |

网友评论