ВЂааNOR FlashдкSOPCПЊЗЂжаЕФгІгУ

ЗЂВМЪБМфЃК2010-6-4 16:49

ЗЂВМепЃКРюПэ

|

в§бд ЫцзХFPGAММЪѕЕФЗЂеЙЃЌГіЯжСЫвЛжжаТИХФюЕФЧЖШыЪНЯЕЭГЃЌМДSOPCЃЈSystem On Programmable ChipЃЉЁЃSOPCММЪѕШкКЯСЫSoCКЭFPGAЕФгХЕуЃЌНЋДІРэЦїЁЂЦЌЩЯзмЯпЁЂЦЌЩЯДцДЂЦїЁЂФкВПЭтЩшЁЂI/OНгПквдМАздЖЈвхТпММЏГЩдкЭЌвЛЦЌFPGAжаЃЌЖјЧвШэгВМўПЩВУМєЁЂПЩЩ§МЖЁЂПЩаоИФЃЌОпгаШэгВМўдкЯЕЭГБрГЬФмСІЃЌдкБЃжЄИпадФмЕФЭЌЪБОпгаЗЧГЃИпЕФСщЛюадЁЃгЩгкДѓВПЗжЙІФмВПМўдкFPGAФкЪЕЯжЃЌЭтВПжЛашвЊКмЩйЕФЦїМўЃЌШчДѓШнСПЕФRAMЁЂFlashЁЂDACЁЂADCЕШЁЃдкЯЕЭГашвЊЭбРыМЦЫуЛњЖРСЂдЫааЪБЃЈОјДѓВПЗжЧщПіШчДЫЃЉЃЌЗЧвзЪЇЕФДцДЂЦїМўFlashЪЧБиВЛПЩЩйЕФЁЃFlashПЩвдгУРДДцДЂХфжУБШЬиСїЁЂДњТыЁЂЪ§ОнЛђВЮЪ§ЕШживЊаХЯЂЁЃБОЮФвдIntel StrataFlash 3V MemoryЯЕСаЕФJS28F128J3D75ВЂааNOR FlashЃЈМђГЦЁАJ3DЁБЃЉКЭXilinx FPGA Spartan3EЯЕСаЕФXC3S1600EЃЈМђГЦЁА1600EЁБЃЉЮЊБГОАЃЌдкНсКЯЯюФППЊЗЂОбщКЭВЮдФЯрЙиЮФЯзЕФЛљДЁЩЯЃЌНщЩмСЫВЂааNOR FlashдкSOPCПЊЗЂжаЕФ4жжВЛЭЌгІгУЁЃ 1 ДцДЂFPGAХфжУБШЬиСї 1600EЙЄзїдкBPIЃЈBytewide Peripheral InteRFaceЃЉХфжУФЃЪНЪБЃЌЭЈЙ§зЈУХЕФв§НХгыJ3DСЌНгЃЌетаЉв§НХдкХфжУЭъГЩКѓПЩвдзїЮЊгУЛЇI/OЪЙгУЁЃСЌНгЪБЃЌДѓВПЗжв§НХВЮПМ1600EЕФЪ§ОнЪжВсжБНгСЌНгМДПЩЃЌЕЋгааЉв§НХашвЊЬиБ№зЂвтЁЃJ3DгаЁС8ЃЈЪ§ОнзмЯпПэЖШЮЊ8ЮЛЃЉКЭЁС16ЃЈЪ§ОнзмЯпПэЖШЮЊ16ЮЛЃЉСНжжЙЄзїФЃЪНЁЃХфжУЪБгІЙЄзїдкЁС8ФЃЪНЃЌХфжУЭъГЩКѓЃЌИљОнашвЊПЩвдЩшжУЮЊЁС8ЛђЁС16ФЃЪНЁЃЭМ1ЮЊ1600EгыJ3Dв§НХСЌНгЪОвтЭМЁЃ

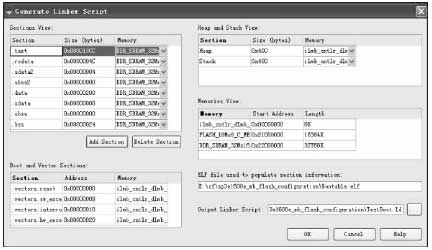

ЭМ1 1600EгыJ3Dв§НХСЌНгЪОвтЭМ ШєХфжУКѓашвЊЧаЛЛжСЁС16ФЃЪНЃЌдђашзлКЯПМТЧ1600EЕФHSWAPНХЁЃHSWAPНгИпЕчЦНЪБЃЌ1600EЫљгагУЛЇI/OЕФФкВПЩЯРЕчзшНћгУЃЌHDCЭЈЙ§4.7kІИЕчзшНгИпЕчЦНЃЌLDC2ЭЈЙ§4.7 kІИЕчзшНгЕиЃЌLDC1КЭLDC0ЭЈЙ§4.7kІИЕчзшНгИпЕчЦНЃЌЭЌЪБет3ИіаХКХгІЗжБ№СЌЕНJ3DЕФBYTE#ЁЂOE#ЁЂCE0НХЁЃетбљЩЯЕчКѓЕФЫВМфЃЌJ3DЙЄзїдкЁС8ФЃЪНЃЌЧввђCE0НХБЛРИпЖјДІгкЗЧбЁжазДЬЌЃЌВЛЛсЕМжТЖдJ3DЕФЮѓВйзїЃЛШЛКѓдк1600EЕФПижЦЯТНјШыХфжУзДЬЌЃЌХфжУНсЪјПЩЭЈЙ§ПижЦ LDC2ЪфГіИпЕчЦНЖјНЋJ3DЧаЛЛЮЊЁС16ФЃЪНЁЃHSWAPНгЕЭЕчЦНЪБЃЌ1600EЫљгагУЛЇI/OЕФФкВПЩЯРЕчзшЪЙФмЃЌLDC1ЁЂLDC0КЭHDCЮоашЭтНгЩЯРЕчзшЃЛЖјLDC2гІНг340ІИЕФЯТРЕчзшЃЌвдЪЙЩЯЕчКѓJ3DЙЄзїдкЁС8ФЃЪНЃЌДгЖјЫГРћНјШыХфжУзДЬЌЃЌХфжУНсЪјКѓПЩНЋJ3DЧаЛЛЮЊЁС16ФЃЪНЁЃ ШєХфжУКѓЙЄзїдкЁС8ФЃЪНЃЌдђJ3DЕФBYTE#НХНгЕЭЕчЦНЃЌ1600EЕФLDC2аќПеЁЃЕБHSWAPНгИпЕчЦНЪБЃЌLCD1КЭLCD0ЗжБ№СЌжСOE#ЁЂ CE0НХЃЌЭЌЪБгІЭЈЙ§4.7kІИЕчзшЩЯРЃЛHSWAPНгЕЭЕчЦНЪБЃЌLCD1КЭLCD0ВЛгУЩЯРЁЃ ХфжУБШЬиСїЮФМўЪзЯШЭЈЙ§iMPCTзЊЛЛГЩMCSЮФМўЃЌдйЭЈЙ§PicoBlaze NOR Flash ProgrammerЃЈhttp://www.xilinx.com/products/boards/s3estarter/files /s3esk_picoblaze_nor_flash_programmer.zipЃЉЯТдиЕНJ3DжаЁЃ J3DПЩвдЭЌЪБХфжУЖрПщ FPGA,вВПЩЖдЭЌвЛПщFPGAНјааЖрБШЬиСїХфжУЁЃР§ШчЯШХфжУвЛИіеяЖЯВтЪдБШЬиСїЃЌВтЪдГЩЙІКѓЃЌдйжиаТХфжУгІгУБШЬиСїЁЃ 2 ДцДЂПЩв§ЕМЕФШэДІРэЦїДњТы ЪзЯШРћгУXilinxЧЖШыЪНПЊЗЂЙЄОпЯфEDKДДНЈвЛИіЧЖШыЪНЙЄГЬЃЌАќРЈ MicroBlazeгВМўЦНЬЈКЭЯргІЕФШэМўЙЄГЬЁЃдкEDKНчУцЯТЃЌгУЪѓБъбЁжаДДНЈЕФШэМўЙЄГЬЃЌгвЛїВЂдкЕЏГіЕФВЫЕЅжабЁдёGenerate Linker Script...ЯюЃЌНјШыGenerate Linker ScriptЖдЛАПђЁЃНЋSectionsЁЂHeapКЭStackжИЖЈЕНBRAMЛђЭтВПRAMЃЈвЛАуНЋHeapКЭStackжИЖЈЕНBRAMЃЌДњТыКЭЪ§ОнЖЮжИЖЈЕНЭтВПRAMЃЉЃЌВЂжИЖЈЪфГіНХБОЮФМўУћМАТЗОЖЃЌШчЭМ2ЫљЪОЁЃ

ЭМ2 Generate Linker ScriptЖдЛАПђ ЫЋЛїЯргІШэМўЙЄГЬЯТЕФCompiler OptionsбЁЯюЃЌНјШыSet Compiler OptionsЖдЛАПђЃЌЩшЖЈLink ScriptЯюЮЊИеВХВњЩњЕФНХБОЮФМўЃЌВЂжИЖЈOutput ELF FileЯюЕФТЗОЖгыУћГЦЁЃЯждкПЩвдБрвыЯргІЕФШэМўЙЄГЬЃЌВњЩњЯргІЕФПЩжДааELFЮФМўЃЌЩшЮЊBootable.elfЁЃ дкEDKжїНчУцЯТЃЌгУЪѓБъбЁдёDevice Configuration Ёњ Program Flash Memory,НјШыProgram Flash MemoryЖдЛАПђЃЌВЂАДЭМ3НјааЩшжУЁЃЕЅЛїOKАДХЅЃЌЛсАбBootable.elfЮФМўздЖЏзЊЮЊSRECИёЪНЃЌВЂЯТдиЕНJ3DЕФжИЖЈЕижЗДІЃЌЭЌЪБВњЩњУћЮЊbootloadr_0ЕФШэМўЙЄГЬЁЃbootloadr_0ЙЄГЬБрвыКѓВњЩњЕФПЩжДааЮФМўexecutable.elfгУРДжДаав§ЕМзАдиЙІФмЃЌгІНЋЦфКЯВЂЕНЯЕЭГБШЬиСїsystem.bitЃЌДгЖјЩњГЩdowload.bitЁЃdowload.bitОiMPCTзЊЮЊMCSЮФМўКѓЯТдиЕНХфжУPROMжаЃЈШєЪЙгУЭЌвЛЦЌJ3DЃЌзЂвтВЛФмгыBootable.elfЗЂЩњЕижЗПеМфГхЭЛЃЉЁЃетбљЃЌЯЕЭГЩЯЕчКѓЃЌЪзЯШЖдFPGAНјааХфжУЃЌШЛКѓв§ЕММгдиJ3DжаЕФДњТыжСЯргІЕФ BRAMЛђSDRAMжаЃЈОпЬхгГЩфЮЛжУвбдкGenerate Linker ScriptЖдЛАПђжаЩшЖЈЃЉЁЃ

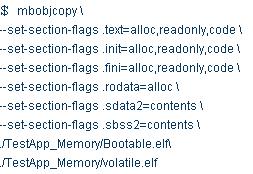

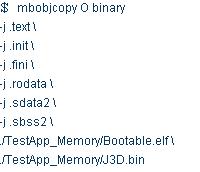

ЭМ3 Program Flash MemoryЖдЛАПђ 3 ДцДЂПЩжБНгжДааЕФШэДІРэЦїДњТы етРяШдШЛЪЙгУЩЯУцДДНЈЕФEDKЙЄГЬЃЌгЩгкJ3DОпгаРрЫЦ SRAMЕФНгПкЃЌЩЯЕчКѓПЩвджБНгЯёSRAMвЛбљНјааЖСВйзїЃЌЕЋШДВЛФмжБНгНјаааДВйзїЁЃвђДЫЃЌгІНЋжЛЖСЖЮ.codeЁЂ.rodataЁЂ.sdata2ЁЂ.sbss2жИЖЈЕНJ3DжаЃЌЦфгрЖЮжИЖЈЕНBRAMжаЃЌетПЩвддкGenerate Linker ScriptЖдЛАПђжаЭъГЩЁЃжиаТБрвыКѓЩњГЩаТЕФBootable.elfЮФМўЁЃДЫЪБЃЌBootable.elfШдЪЧвЛИіећЬхЃЌашвЊНЋЦфдкЮяРэЩЯЗжЮЊ2ИіЮФМўЃКвЛИіДцЗХжЛЖСЖЮЃЌСэвЛИіДцЗХЦфгрЖЮЁЃОпЬхПЩвдЭЈЙ§ЯТУцЕФВйзїЪЕЯжЁЃ Ђй ДДНЈДцДЂдкBRAMжаЕФОЕЯёvolatile.elfЁЃдкXPSжаЃЌбЁдёProject Ёњ Launch EDK ShellЃЌВЂжДааЯТСаУќСю:

Ђк ДДНЈДцДЂдкFlashжаЕФОЕЯёJ3D.binЁЃдкXPSжаЃЌбЁдёProject Ёњ Launch EDK

НЋvolatile.elfКЯВЂЕНЯЕЭГХфжУБШЬиСїsystem.bitЃЌЩњГЩ dowload.bitЃЌдйОiMPCTзЊЮЊMCSИёЪНКѓЯТдиЕНХфжУPROMжаЁЃдйНЋJ3D.binЭЈЙ§Program Flash MemoryЖдЛАПђЯТдиЕНJ3DжаЁЃетбљЯЕЭГЩЯЕчВЂЭъГЩХфжУКѓЃЌJ3DжаЕФДњТыЮоашв§ЕМБуПЩвджБНгжДааЁЃ 4 ДцДЂЗЧвзЪЇЪ§ОнЛђВЮЪ§ гаЪБКђЯЕЭГашвЊДцДЂЗЧвзЪЇЕФЪ§ОнЛђВЮЪ§ЃЌетОЭашвЊЭЈЙ§БраДГЬађжБНгЖдJ3DНјааЖС/аДВйзїЁЃЕБШЛЃЌЧАЬсЪЧЯШвЊдкEDKжаЮЊJ3DЬэМгвЛИіXPS MCH EMCНгПкЁЃетИіНгПкЖдВЂааNOR FlashКЭSRAMРДЫЕЖМЪЧЪЪгУЕФЃЌШчЙћгУгкSRAMдђПЩвджБНгЖС/аДЃЌВЛашвЊЧ§ЖЏЃЌЖјгУгкВЂааFlashдђашвЊздМКБраДЯргІЕФЧ§ЖЏГЬађЁЃЯТУцЮЊздааБраДЕФвЛИіжДааПщВСГ§ЁЂЕЅзжаДЁЂЕЅзжЖСВйзїЕФГЬађЁЃашвЊзЂвтЕФЪЧЃКаДВйзїЧАвЛЖЈвЊЯШНјааВСГ§ВйзїЃЌаДУќСюЛђаДЪ§ОнжЎКѓвЛЖЈвЊЖдзДЬЌМФДцЦїНјааХаЖЯЪЧЗёЭъГЩЯргІВйзїЃЛЖСВйзїдђКмМђЕЅЃЌЯёSRAMЕФЖС/аДвЛбљЁЃ

ЛЙгавЛжжЧщПіЪЧдкЯЕЭГдЫааЧАОЭАбЪ§ОнаДШыFlashжаЁЃЪзЯШЃЌАбЪ§ОнаДШывЛИіЖўНјжЦЮФМўжаЁЃзЂвтЃЌMicroBlazeЕФДцДЂИёЪНЪЧBigEndianЃЈМДИпзжНкЪ§ОнБЃДцдкЕЭЕижЗЃЌЕЭзжНкЪ§ОнБЃДцдкИпЕижЗЃЉЃЌPCЛњЕФДцДЂИёЪНдђЪЧ LittleEndianЃЈМДИпзжНкЪ§ОнБЃДцдкИпЕижЗЃЌЕЭзжНкЪ§ОнБЃДцдкЕЭЕижЗЃЉЃЌвђДЫШчЙћЪЧгУVC++ВњЩњЕФЖўНјжЦЮФМўЃЌвЛЖЈвЊНјааИпЁЂЕЭзжНкНЛЛЛЁЃдк MatlabжаЩњГЩЪ§ОнЮФМўдђПЩвддкЯргІЕФЮФМўВйзїКЏЪ§жаЬэМгВЮЪ§'b'ЃЈБэЪОвдBigEndianИёЪНДцДЂЃЉЃЌШч FileID=fopen('data.bin','w+','b')ЁЃВњЩњЕФЖўНјжЦЮФМўПЩвдЭЈЙ§Program Flash MemoryЖдЛАПђЯТдиЕНJ3DжаЃЌзЂвтВЛвЊбЁжаAuto?convert file to SREC format when programming flashКЭCreate Flash Bootloader ApplicationбЁЯюЁЃ Нсгя БОЮФЬжТлСЫдквдXilinx Spartan XC3S1600EЮЊЛљДЁЕФSOPCЩшМЦжаЃЌIntel J3DВЂааNOR FlashЕФ4жжВЛЭЌгУЭОМАЦфЪЙгУЗНЗЈгыММЧЩЃЌгШЦфЖдвЛаЉММЪѕЙиМќЮЪЬтгшвдЯъЯИЕФВћЪіЃЌЦфжаШкШыСЫБЪепдкЯюФППЊЗЂжаЕФЪЕМЪОбщЃЌОпгаНЯИпЕФВЮПММлжЕЁЃ J3DМШПЩвдгУгкДцДЂFPGAХфжУБШЬиСїЃЌгжПЩвдДцДЂШэДІРэЦїГЬађДњТыЃЌвВПЩвдДцДЂЗЧвзЪЇЕФЪ§ОнКЭВЮЪ§ЃЌЩѕжСШ§епПЩвдВЂДцгкЭЌвЛЦЌJ3DжаЁЃБОЮФжЛЪЧвд Intel J3DВЂааNOR FlashЮЊР§ЬжТлЦфдкSOPCПЊЗЂжаЕФгУЗЈЃЌетаЉЗНЗЈЭЌбљЪЪгУгкЦфЫћГЇМвОпгаCFIЃЈCommon Flash InteRFaceЃЉНгПкЕФВЂааNOR FlashЁЃСщЛюЕизлКЯдЫгУетаЉЗНЗЈЃЌЖдгкSOPCПЊЗЂОпгаживЊвтвхЁЃ ВЮПМЮФЯз ЁЁЁЁ[1] бІаЁИеЃЌИ№вуУє.Xilinx ISE 9.x FPGA/CPLDЩшМЦжИФЯ[M].ББОЉЃКШЫУёгЪЕчГіАцЩчЃЌ2007. ЁЁЁЁ[2] Ying Sue.Connecting Intel StrataFlash to Memory to Spartan3E FPGAs,2005. ЁЁЁЁ[3] Intel Inc.Intel Embedden Flash Memory(J3 v.D),200702. ЁЁЁЁ[4] Xilinx Inc.Spartan3E FPGA Family:Complete Data Sheet,20070529. ЁЁЁЁ[5] Xilinx Inc. Executing and Debugging Software FromFlash Memory,20070924. зїепЃКедЗЩ Эѕбз (ЖЋФЯДѓбЇ) ИЖшЄ (НЫеЬьБІЦћГЕЕчзггаЯоЙЋЫО) РДдДЃКЕЅЦЌЛњгыЧЖШыЪНЯЕЭГгІгУ 2008 (9) |

ЭјгбЦРТл