Xilinx UltraScale:为您未来架构而打造的新一代架构

发布时间:2013-7-18 16:33

发布者:eechina

|

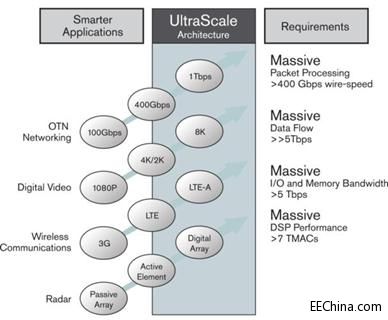

Xilinx UltraScale 架构针对要求最严苛的应用,提供了前所未有的ASIC级的系统级集成和容量。 UltraScale架构是业界首次在All Programmable架构中应用最先进的ASIC架构优化。该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。借助Xilinx Vivado设计套件的分析型协同优化,UltraScale架构可以提供海量数据的路由功能,同时还能智能地解决先进工艺节点上的头号系统性能瓶颈。这种协同设计可以在不降低性能的前提下达到实现超过90%的利用率。 UltraScale架构的突破包括: • 几乎可以在晶片的任何位置战略性地布置类似于ASIC的系统时钟,从而将时钟歪斜降低达50% • 系统架构中有大量并行总线,无需再使用会造成时延的流水线,从而可提高系统速度和容量 • 甚至在要求资源利用率达到90%及以上的系统中,也能消除潜在的时序收敛问题和互连瓶颈 • 可凭借3D IC集成能力构建更大型器件,并在工艺技术方面领先当前行业标准整整一代 • 能在更低的系统功耗预算范围内显著提高系统性能,包括多Gb串行收发器、I/O以及存储器带宽 • 显著增强DSP与包处理性能 赛灵思UltraScale架构为超大容量解决方案设计人员开启了一个全新的领域。 越多越好 自从“全面数字化”(all things digital)概念引入以来,“越多越好”成为了所有市场领域中数字系统的一种基本的、必然的发展趋势。这一期望成为了促使系统要求更高分辨率、更高带宽和更大存储量的基本动力。而“更多”这一理念同时从逻辑上也引发了如下事实的产生: • 更多的器件生成更多数据。 • 更多的数据意味着数据必须更快流动。 • 更多快速流动的数据要求计算速度更快。 • 更多的应用需要更快速地访问更多数据。 • 数据量的增长和数据速率的提高对数据完整性提出了更高要求。 目前几乎每个领域的数据创建和数据传输速率都在快速增长,这会加大对新型器件架构的需求,以应对如下问题所带来的重重挑战: • 海量数据流以及类似于ASIC的时钟布线 • 海量I/O和存储器带宽 • 更快的DSP和包处理 • 电源管理 • 多级安全 UltraScale架构:赛灵思的新一代All Programmable架构 为了达到每秒数百Gb的系统性能和全线速下的智能处理能力,并扩展到Tb级和每秒万亿次浮点运算,需要采用一种新的架构方案。为此,我们要做的不仅仅是简单地提高每个晶体管或系统模块的性能,或扩展系统中的模块数量,而是要从根本上改善通信、时钟、关键路径和互连功能,以满足海量数据流、实时数据包和图像处理需求。 UltraScale™ 架构通过在一个全面可编程(All Programmable)架构中应用最先进的ASIC 技术,可应对上述需要海量I/O和存储器带宽、海量数据流以及卓越DSP和包处理性能的挑战。。UltraScale架构经过精调可提供大规模布线能力并且与Vivado®设计工具进行协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。 UltraScale架构是业界首次在All Programmable架构中应用最先进的ASIC架构优化该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈,即互连问题。 Xilinx UltraScale架构旨在满足下一代系统级性能要求。(见图1)

图1:下一代高性能目标应用范例 赛灵思对UltraScale架构进行了数百项设计提升,并将这些改进实现有机结合,让设计团队能够打造出比以往功能更强、运行速度更快、单位功耗性能更高的系统。见图2。

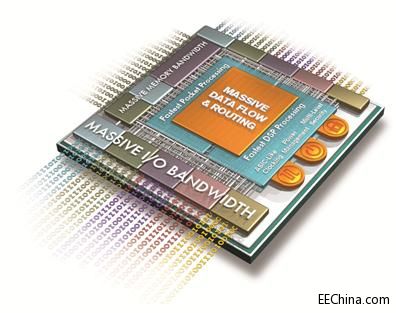

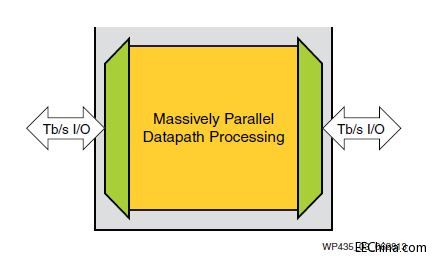

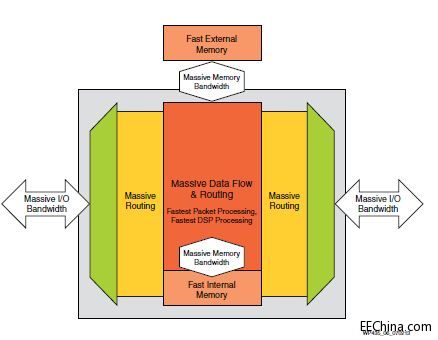

图2:Xilinx UltraScale架构 UltraScale架构与Vivado™设计套件结合使用可提供如下这些新一代系统级功能: • 针对宽总线进行优化的海量数据流,可支持数Tb级吞吐量和最低时延 • 高度优化的关键路径和内置高速存储器,级联后可消除DSP和包处理中的瓶颈 • 增强型DSP slice包含27x18位乘法器和双加法器,可以显著提高定点和IEEE 754标准浮点算法的性能与效率 • 第二代3D IC系统集成的晶片间带宽以及最新3D IC宽存储器优化接口均实现阶梯式增长 • 类似于ASIC的多区域时钟,提供具备超低时钟歪斜和高性能扩展能力的低功耗时钟网络 • 海量I/O和存储器带宽,用多个硬化的ASIC级100G以太网、Interlaken和PCIe® IP核优化,可支持新一代存储器接口功能并显著降低时延 • 电源管理可对各种功能元件进行宽范围的静态与动态电源门控,实现显著节能降耗 • 新一代安全策略,提供先进的AES比特流解密与认证方法、更多密钥模糊处理功能以及安全器件编程 • 通过与Vivado工具协同优化消除布线拥塞问题,实现了90%以上的器件利用率,同时不降低性能或增大时延 系统设计人员将这些系统级功能进行多种组合,以解决各种问题。下面的宽数据路径方框图可以很好地说明这一问题。见图3.

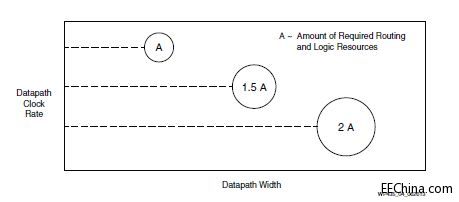

图3:Tb级I/O需要海量的并行数据路径 图中,数据速率高达Tbps的数据流从从左侧流入再从右侧流出。系统必须在左右两侧的I/O端口之间传输数据流,同时还要执行必要的处理工作。可以通过高速串行收发器来进行I/O传输,运行速率高达数Gbps。一旦数Gbps的串行数据流进入器件,就必须扇出(fan out),以便与片上资源的数据流、路由和处理能力相匹配。 Tb级系统的设计挑战:时钟歪斜与海量数据流 举一个现实的实例,假设左侧和右侧I/O端口的带宽为100Gb/s。这意味着片上资源也必须要处理至少100Gb/s的流量。设计人员一般采用512至1024位的宽总线或数据路径来处理相关的数据吞吐量,产生一个与片上资源功能相匹配的系统时钟。如果线速提高到400Gb/s,那么总线宽度达到1024至2048位也并不少见。 现在考虑一下这类总线的时钟要求。在UltraScale架构推出之前,高系统时钟频率运行会使这些海量数据路径上的时钟歪斜程度增大,甚至达到整个系统时钟周期的将近一半。时钟歪斜几乎占用一半的时钟周期,这种情况下设计方案需要依靠大量流水线才有可能达到目标系统性能。只剩下一半的时钟周期可用于计算,因此得到可行解决方案的几率就会很低。大量使用流水线不仅会占用大量寄存器资源,而且还会对系统的总时延造成巨大影响,这也再次证明了这种方法在当今的高性能系统中不可行。 UltraScale架构提供类似ASIC时钟功能 多亏UltraScale 架构提供类似ASIC的多区域时钟功能,使得设计人员现在可以将系统级时钟放在整个晶片的任何最佳位置上,从而使系统级时钟歪斜降低多达50%。将时钟驱动的节点放在功能模块的几何中心并且平衡不同叶节点时钟单元(leaf clock cell)的时钟歪斜,这样可以打破阻碍实现多Gb系统级性能的一个最大瓶颈。系统总体时钟歪斜降低后,就无需再使用大量流水线,并可消除随之而来的时延问题。UltraScale架构中类似于ASIC的时钟功能不仅能移除时钟布置方面的限制,还能在系统设计中实现大量独立的高性能、低歪斜时钟源。这与前几代可编程逻辑器件中所采用的时钟方案完全不同。从系统设计人员的角度出发,这种解决方案能轻松解决时钟歪斜问题。 从容应对海量数据流挑战 极高性能应用一般采用宽总线或宽数据路径来匹配路由到片上处理资源的数据流。然而采用宽总线来扩展性能时,除了要简单处理时钟歪斜问题外,还要应对一系列自身挑战。众所周知,同类竞争架构经证实其适用于高性能设计的布线资源非常有限且缺乏灵活性。如果FPGA的互连架构性能较低,那么用它来实现100Gb/s吞吐量的应用时,需要将数据总线提升到1536至2048位的宽度。 尽管更宽的总线实现方案可以降低系统时钟频率,但由于缺乏支持宽总线系统所需的布线资源,因此会产生严重的时序收敛问题。而且有些FPGA厂商采用的是过时的模拟退火布局布线算法,不考虑拥塞程度和总线路长度等全局设计指标,因此会进一步加剧时序收敛问题。这样,设计人员就不得不进行多方面权衡,包括降低系统性能(通常不可取);使用大量流水线,不惜增大时延;或者降低可用器件资源利用率。在任何情况下,经证明这些解决方案都是不佳或存在欠缺的方案。最重要的是,传统FPGA中布线资源(用于满足100Gb/s应用的要求)的局限性几乎可以说明它们不可能适用新一代多Tb应用的要求,即便能适用,但器件的利用率会非常低,时延极高。 更为复杂的问题在于,通过大量的宽数据总线来扩展性能会带来额外的代价,那就是需要显著增加逻辑电路开销用以支持宽总线的实施,从而进一步加大实现时序收敛的难度。 以以太网数据包大小为例可以很好地说明这个情况。以太网的数据包最小为64字节(512位)。假设采用2048位宽的总线来实现400G的系统,那么总线最多容纳4个数据包。 在2048位宽的总线中存在多种数据包组合形式,例如4个完整数据包或者1个、2个或3个完整或部分数据包,这样需要使用大量逻辑来处理不同的情况与组合。需要大量复杂的重复逻辑来应对这些可能的组合。此外,如果总线要求对四个数据包进行同时处理并写入到存储器中,那么可能需要对逻辑的某些部分进行加速(或扩展性能)。可以考虑通过逻辑加速或用四个独立的相同存储器控制器来相继处理多个数据包,但这些方式会进一步加大布线资源的压力,迫使架构必须具备更多的高性能、低歪斜布线资源。参见图4。

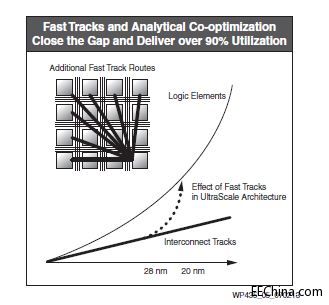

图4:增加数据路径时钟宽度和时钟速率需要更多逻辑和布线资源 半导体工艺的扩展影响互连技术 随着业界向20nm或更高级半导体工艺技术推进,在与铜线互连有关的RC延迟方面出现了新的挑战,它会阻碍向新工艺节点演进所实现的性能提升效果。晶体管互连延迟的增加会直接影响所能实现的总体系统性能,因此更加需要所使用的布线架构能提供满足新一代应用要求的性能等级。UltraScale布线架构在开发过程中充分考虑了新一代工艺技术的特点,而且能明显减轻铜线互连的影响——如不进行妥善处理会成为系统性能瓶颈。 UltraScale互连架构:针对海量数据流进行优化 UltraScale新一代互连架构的推出体现了可编程逻辑布线技术的真正突破。赛灵思致力于满足从多Gb智能包处理到多Tb数据路径等新一代应用需求,即必须支持海量数据流。在实现宽总线逻辑模块(将总线宽度扩展至512位、1024位甚至更高)的过程中,布线或互连拥塞问题一直是影响实现时序收敛和高质量结果的主要制约因素。过于拥堵的逻辑设计通常无法在早期器件架构中进行布线;即使工具能够对拥塞的设计进行布线,最终设计也经常需要在低于预期的时钟速率下运行。而UltraScale布线架构则能完全消除布线拥塞问题。结论很简单:只要设计合理,就能进行布线。 我们来做个类比。位于市中心的一个繁忙十字路口,交通流量的方向是从北到南,从南到北,从东到西,从西到东,有些车辆正试图掉头,所有交通车辆试图同时移动。这样通常就会造成大堵车。现在考虑一下将这样的十字路口精心设计为现代化高速公路或主干道,情况又会如何。道路设计人员设计出了专用坡道(快行道),用以将交通流量从主要高速路口的一端顺畅地疏导至另一端。交通流量可以从高速路的一端全速移动到另一端,不存在堵车现象。 赛灵思为UltraScale架构加入了类似的快行道。这些新增的快行道可供附近的逻辑元件之间传输数据,尽管这些元件并不一定相邻,但它们仍通过特定的设计实现逻辑上的连接。这样,UltraScale架构所能管理的数据量就会呈指数级上升,如图5所示。

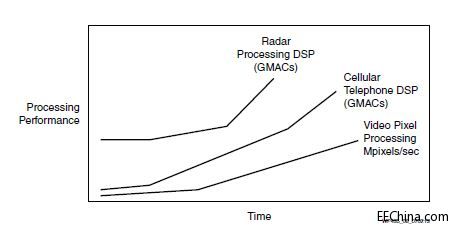

图5:增加真实有效的路由路径可以帮助解决日益增长的系统复杂性 UltraScale架构堆叠硅片互联技术全面强化所有功能 很少有开发的技术能够像堆叠硅片互联(SSI)技术集成那样对器件容量和性能产生如此重大的影响,这已得到了赛灵思第一代基于7系列All Programmable器件的3D IC产品的验证。集成SSI技术后,设计人员可以构建出工艺技术领先行业标准整整一代水平的更大型器件。而且该技术在赛灵思第二代基于UltraScale架构的3D IC产品中也同样会达到这种效果。 由于3D IC中硅片间通信连接比独立封装的硅片间通信连接更密集、更快速,因此硅片间的通信所需功耗更低(假设硅片无需驱动硅片到封装间互连以及板级互连的附加阻抗)。所以,与独立封装的硅片相比,SSI技术的集成能够在显著扩大容量和性能的同时降低功耗。此外,由于无法轻易访问电路板层面的硅片间通信,这样系统安全性也得到了加强。 Virtex®UltraScale和Kintex®UltraScale系列成员在第二代3D IC中的连接资源数量以及相关的硅片间带宽都实现了阶梯式增长。布线资源和硅片间带宽的大幅增长确保了新一代应用能够在实现其高器件利用率的前提下达到目标性能和时序收敛。 智能、快速处理的挑战 对于任何高性能系统来说,无论目标是提高数据包吞吐量,还是增大DSP GMAC,亦或是增加屏幕的每秒显示像素,所面临的技术挑战都是相同的,如图6所示。

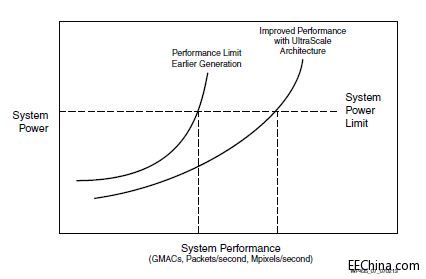

图6:高性能系统需要海量的数据带宽 无论对于哪种应用,问题描述起来都很简单,即大量数据以数十至数百GB的速度通过多个高速串行端口进入系统。应将这些高速数据路由到处理逻辑并进行实时处理,这一般要求采用较高的DSP或包处理速度来应对高数据速率。输入数据和中间处理结果数据必须存储在系统中或靠近处理元件的地方,或者存放在与系统临近的大容量存储器内。数据经过处理后,必须路由至高速输出收发器进行发送。如图6所示: • 通过高速串行线路实现系统数据的输入和输出要求利用可靠的多Gb串行收发器实现很高的I/O带宽。串行收发器必须可靠并具备非常低的误码率。 • 大量并行布局线路从多Gb串行收发器扇出至广泛的功能处理模块,这需要通过低时钟歪斜的宽扇出能力才能实现。布置大量并行总线的难度比较大。 • 要对海量数据流进行处理,就要采用高吞吐量的逻辑模块和DSP模块,并要通过高带宽存储器接口实现非常快速的内部与外部存储器访问能力。这种处理需求对任何架构的数据与时钟布线功能都来说都是一种严峻的考验。 必须在一定的功耗范围内满足所有性能指标。系统必须在有限的功耗和冷却限值内运行,如图 7概念图所示。

图7:UltraScale架构超越了早期的功耗和性能限制 UltraScale架构的组成部分针对新一代处理系统的众多复杂要求进行了调整。 提供海量I/O和存储器带宽 UltraScale架构能在显著增强高速SerDes收发器性能的同时大幅降低其功耗。Virtex UltraScale器件采用可支持5 Tbps以上串行系统带宽的新一代SerDes(收发器)。 基于UltraScale架构的GTY和GTH串行收发器包含内部变速箱(gearbox)逻辑,用于将多Gb/s的串行数据线速率转化成更宽的数据总线(几百MHz),以便与片上逻辑和存储器速度相匹配。收发器的gearbox能消除在系统设计中因使用外部gearbox芯片而带来的成本。与之类似的是,基于UltraScale架构的GTY串行收发器所采用的集成分数锁相环(PLL)能够将一个参考时钟转换成多个线路速率,因此无需再使用外部的电压控制型晶体振荡器(VCXO)。仅这一项功能就可以节省数十个分立器件,并为采用众多不同线路速率高速串行端口的系统设计节省数百美元。 采用UltraScale架构的ASIC级串行收发器与早期器件中的收发器相比具备更高的灵活性,同时保留了赛灵思7系列ALL Programmable器件可靠的自适应均衡功能(自动增益控制、连续时间线性均衡、决策反馈均衡)。赛灵思的自适应均衡功能可以将误码率维持在无法检测到的水平(例如小于10-17),并允许基于UltraScale架构的收发器直接驱动数GHz的高速背板。 提供超高的外部与内部存储器带宽 UltraScale架构能支持多个适用于DDR3/4的SDRAM存储控制器,并包含硬化的DDR物理层(PHY)片上模块,从而将存储器接口性能提升到了新高度。与早期器件相比,基于UltraScale架构的器件具备如下优势: • 更多SDRAM控制器 • 更宽的SDRAM端口 • 更快的存储器端口 因此,基于UltraScale架构的All Programmable器件能提供超过1 Tb/s的DDR SDRAM存储器带宽,用以满足领先的新一代系统设计提出的海量数据流、快速处理和超大存储器等要求。与软核PHY相比,硬化的SDRAM PHY模块能将读取时延降低30%,同时该模块能控制DDR4 SDRAM,从而将用于外部存储器的功耗降低20%以上。 片上Block RAM性能往往是影响系统最大时钟速率的关键因素。赛灵思已对UltraScale架构All Programmable器件中的Block RAM进行了重新设计,以便在降低功耗的同时与系统中其他可编程模块的性能相匹配。新的Block RAM架构支持高速存储器级联,消除了DSP和包处理中存在的瓶颈。输出多路复用器在这种新架构中的使用方式很独特,使得Vivado设计套件工具在无需附加片让布线或逻辑资源的情况下也能高效创建大型、快速的RAM阵列和FIFO。 赛灵思还加强了基于UltraScale架构的Block RAM FIFO配置,以便在相同FIFO上支持不同宽度的输入与输出端口。当FIFO需要从一个系统时钟域跨越到另一个域时(UltraScale架构现在支持很多个时钟域),这项功能很有帮助。 实现快速、智能处理 为满足最终用户要求,DSP和包处理系统的性能需要不断提高,如图8示。

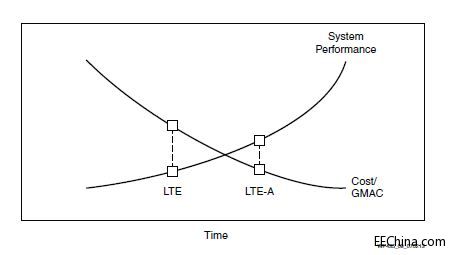

图8:系统性能需要随时间推移而增长 人们需要从噪声中提取更多信号信息;需要创建更加逼真的图像;需要应对无止境的数据包流量增长,所有这些都在对性能提出更高要求。然而,与此同时,还要将成本控制在规定的预算范围内,这样就给设计带来了诸多实际限制。如图9所示,图中描述了LTE和LTE Advanced(LTE-A)基站的性能与成本随时间的变化趋势。

图9:LTE性能和成本发展趋势 简而言之,客户需要以更低成本获得更高的系统性能,这是大多数电子产业永恒不变的趋势,而这也正是UltraScale架构的优势所在。 在领先的性能优势基础之上增强DSP 赛灵思针对UltraScale架构显著增强了已经具备行业最高性能的Virtex-7 FPGA的DSP48E1 DSP slice,以实现更快的数字信号处理能力,同时减少DSP模块外部的布线或逻辑资源使用量。在DSP slice上应用的一系列创新功能可以改善乘法运算和MACC运算,从而增强功能并降低功耗。 基于UltraScale架构的DSP48E2 DSP slice包含27×18位乘法器,可将更大的函数映射到更少的DSP slice中。例如,DSP48E2 block凭借更宽的27×18位乘法器能够以更少的资源实现IEEE Std 754双精度算法,与采用赛灵思7系列All Programmable器件中的DSP48E1模块实现相同功能相比,所采用的DSP模块数量可减少三分之二。 在DSP48E2 slice中包含宽MUX和宽XOR函数后,像错误校正与控制(ECC)、循环冗余校验(CRC)以及前向纠错(FEC)等非DSP运算就可以将DSP slice作为高速、硬化的宽逻辑模块来使用。这些增强特性有助于提高性能,降低功耗,并减少可配置逻辑模块(CLB)的使用量,从而将更多CLB用于实现其他功能。正是通过为DSP等模块增加新功能,UltraScale架构得以同时满足新一代应用对于提高处理能力以及降低成本方面的要求。 扩展的智能数据包处理性能 无止境的带宽需求正持续推高网络通信基础设施的升级投入。数字视频传输所形成的海量数据流加速了100Gb/s网络设备的成熟,同时也加大了对400G解决方案的需求。数据包处理甚至可以给当前业内数百Gb每秒速率的最先进架构带来严峻的性能挑战。在线路速度下执行的校验和计算与桥接等基础数据包处理功能会对性能和资源利用率带来显著影响。 除了解决与高性能数据包处理有关的海量数据流问题外,UltraScale架构还包含多种专为数据包处理定制的创新功能。其中包括:对DSP48模块进行修改以支持线速度下进行的CRC 32校验和计算;加入了硬化的Gb以太网MAC和Interlaken芯片到芯片接口,用以支持智能数据包处理的性能突破和最新的集成等级。 UltraScale架构满足下一代系统级功耗要求 随着系统级性能伴随产品的更新换代而不断得到扩展,人们期望(也是系统要求)功耗也能保持不变或者继续降低。例如,对于有线通信基础设备而言,新一代线路卡必须在不改变外形尺寸或功耗水平的前提下支持更高的带宽或计算性能。尽管我们可能认为这与系统性能提升的本质有一些矛盾(通常来说性能提升必然以功耗增加为代价),但是我们仍可通过系统集成、电源管理策略以及高级工艺技术来持续降低系统功耗。 UltraScale架构为每一代All Programmable系列提供了无可比拟的系统级功耗优势。低功耗的半导体工艺加上芯片和软件上显著的静态、动态功耗门控技术使得总的系统功耗比Xilinx 7系列器件(已经是目前业界功耗最低的可编程逻辑器件)还要低50%。 降低功耗对设计人员来说意味着两件事:(1)更低的功耗预算和散热管理要求;(2)更高的速度。这两点对满足新一代应用不断提高的要求极为重要。 UltraScale的IP保护与防篡改安全功能 几乎在所有市场都在不断加大对赛灵思All Programmable FPGA的使用,以至于这些器件正在成为众多新系统的核心。 赛灵思All Programmable器件的不断普及使得保护器件内的IP与保护器件所处理的数据具有同等重要性。随着安全威胁意识的增长,系统安全领域随即推出了一系列可推动设计安全性不断提高的策略与标准。设计人员在部署需要达到安全标准的产品时,必须考虑众多安全威胁或潜在薄弱环节。简要的薄弱环节列表包括如下内容:大意自满、不完备的安全措施、后门漏洞、设计缺陷、器件缺陷、单粒子翻转、比特流解码、电子欺诈、特洛伊木马、回读、边带信道以及故障插入。 赛灵思的安全解决方案与创新产品已经历了五代以上的发展,UltraScale All Programmable架构在这一基础上引入了多种增强型安全特性,可对载入器件内的IP提供更强的保护并实现防篡改功能,继续保持着延续赛灵思在安全解决方案领域的领先地位。UltraScale 架构在安全性方面的改进包括:更强大更先进的AES比特流解密与认证方案;更多密钥模糊处理功能;确保在编程过程中无法对加密密钥进行外部访问。这样就能得到稳定可靠的业界领先解决方案,满足不断变化的新一代安全要求。 分析协同优化=可预见性的成功 为最严格的应用实现最高水平的集成度、容量和类似于ASIC的系统级性能,仅这一项就已经颇具挑战。而UltraScale架构还从20nm平面FET扩展至16nm鳍式FET甚至更高级的技术,并且从单芯片电路扩展至3D IC,同时还能在不降低性能的前提下实现高达90%的最高器件利用率。满足这些严苛目标的唯一途径就是将UltraScale架构与Vivado设计套件进行协同优化。 Vivado设计套件是一款全新的SoC增强型设计环境,最初针对赛灵思7系列器件推出,主要用于未来十年的All Programmable器件(例如UltraScale架构)。Vivado能解决可编程系统集成与实现方面的关键设计瓶颈,其生产力相对同类竞争开发环境提高了四倍。 要实现新一代设计提出的超高性能、集成度以及结果质量目标,就需要采用全新的器件布局布线方案。传统FPGA布局布线工具依靠模拟退火作为主要的布局优化算法,无法顾及拥塞程度或总导线长度等全局设计指标。要实现具备多Tb性能的设计,需要采用宽总线而且要求时钟歪斜几乎为零。因此,采用模拟退火这种不考虑总体导线长度和拥塞情况的布局布线算法是绝对不可行的。 最佳的布局方案取决于多种因素,例如时序、导线长度和拥塞等标准。 Vivado设计套件利用多变量成本函数找出最优布局方案,这样,设计人员就可以快速确定布线方案,并使器件利用率达到90%以上且不降低性能。与采用其他解决方案相比,这种方式的运行时间更短而且结果的变化程度也更小,这样实现设计收敛所需的迭代次数就更少,并且性能和器件利用率都达到了业界前所未有的高水平。 UltraScale架构与工艺技术 工艺技术在任何芯片架构中都是一个重要的考虑因素,赛灵思UltraScale架构可以支持多种工艺技术。赛灵思与台积(TSMC)合作推出的28nm HPL(低功耗高性能)工艺技术是赛灵思7系列All Programmable器件能够取得巨大成功的主要因素。凭借之前合作所取得的经验,赛灵思与台积又开发出了20nm 20SoC平面工艺技术,用以支持预计将于2013年推出的第一代赛灵思UltraScale All Programmable器件。 然而,赛灵思设计UltraScale架构还有另一个目的,那就是充分利用继20SoC之后的工艺节点16FinFET所提供的更高的性能、容量和节电性能。 另外,在赛灵思“FinFast”开发计划(该计划汇集了赛灵思和台积的优秀工程设计人才)的支持下,赛灵思UltraScale架构和Vivado 设计套件针对台积 16FinFET工艺技术进行了协同优化。这样,赛灵思与台积将于2014年推出第二代UltraScale All Programmable器件芯片。 结论 为了实现数百Gbps的系统级性能,实现全线速智能处理,并扩展至Tbps和每秒万亿次的浮点运算水平,我们需要采用一种全新的架构方案。赛灵思根据新一代高性能系统需求已经开发出了新一代UltraScale 架构和Vivado设计套件。UltraScale架构能提供ASIC级的系统性能,满足最严苛的新一代应用要求:即实现海量I/O和存储器带宽、海量数据流、极高的DSP与包处理性能,并在不影响性能的前提下实现超过90%的前所未有的器件利用率。 UltraScale是业内首款在All Programmable架构中应用最前沿ASIC架构增强功能的产品,能够从20nm平面FET扩展到16nm 鳍式FET,甚至更先进的技术,此外还能从单芯片电路扩展至3D IC。 通过整合台积的先进技术并与Vivado新一代设计套件实现协同优化,赛灵思提前一年实现同类竞争产品1.5倍至2倍的系统级性能与集成度。这相当于我们比竞争对手领先整整一代。 如需了解如何利用UltraScale架构实现您的新一代设计目标,或者详细了解基于UltraScale架构的All Programmable FPGA系列,请联系当地的赛灵思销售办事处或者访问网址 china.xilinx.com。 |

网友评论