2013年度DesignCon大会创新产品回瞻

发布时间:2013-2-5 15:08

发布者:Liming

|

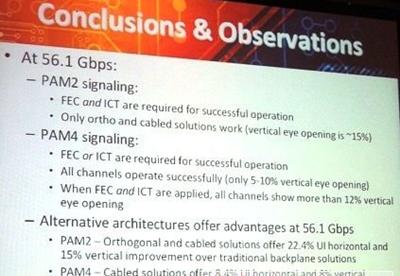

2013年度的 DesignCon 印刷电路板设计大会已经在1月底圆满落幕,与会专家指出,目前的铜线传输速率已经可以达到40Gbps甚至56Gbps;来自 LSI 与 TE Connectivity 等公司的工程师,都展示了不用任何外来技术达到56Gbps速率的模拟。 而专家们也认为,产业界需要更好的材料(如Panasonic的Megtron-6),以及更先进的调变架构(如最新的PAM-2与PAM-4);最值得注意的则是,在印刷电路板与晶片迈向光学时代之前,可能还有至少一个或两个转折点。迈向光学之路不会太容易,还得克服抖动负载的障碍;不过铜线方案还能撑个几年。而IBM、Samtec等公司分别展示了在光学技术方面的进展,为遥远的未来铺路。 在此同时,还有不少引人瞩目的创新成果也在DesgonCon亮相,并有几位优秀的工程师获得奖项鼓励。以下是外媒编辑Rick Merritt在大会现场所收集到的一手影像,来看看这场设计大会上有哪些有趣的东西吧!

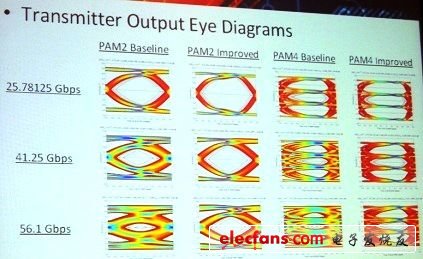

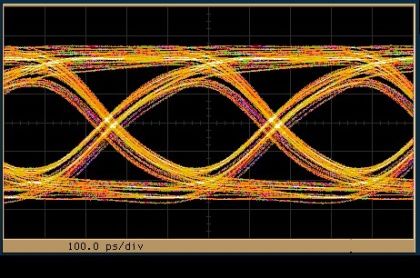

采用新一代调变架构的铜线传输模拟眼图

新一代调变架构PAM-2与PAM-4

Willow Garage出品的精密机器人PR2 是DesignCon展场上的明星,图中是一位试着跟它跳探戈的参观者

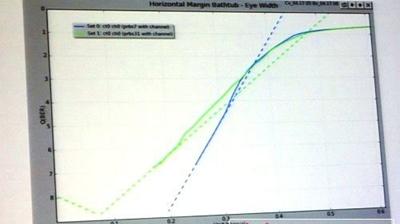

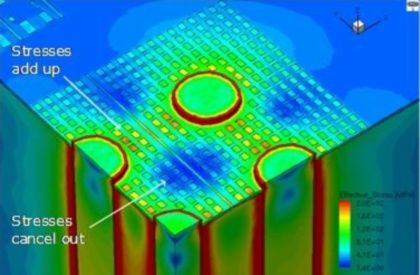

测试工程师描述并量化了一种复杂且不断提高的随机抖动现象,可能会成为25G背板上市的一大障碍

25G背板的测试往往得花上数周时间,测试样本资料长度达到20亿位元;而一位LSI的工程师表示,若将测试样本缩短,所获得的结果有时候会很奇怪地跟较长的样本不同。

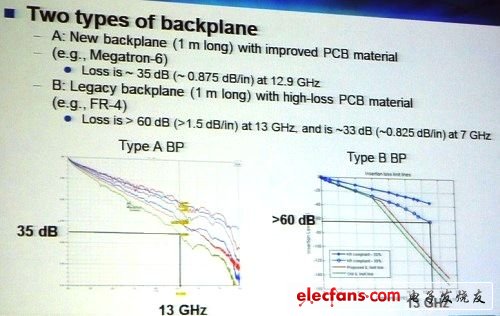

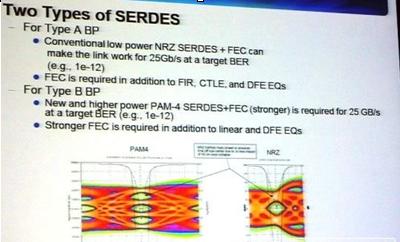

如果想要在高速度之下取得良好的讯号传输结果,可能需要考虑采用如Megtron-6的新材料,或是支援脉冲振幅调变(pulse amplitude modulation)的晶片;Altera工程师Mike Peng 介绍了新一代PCB材料与调变架构的优势

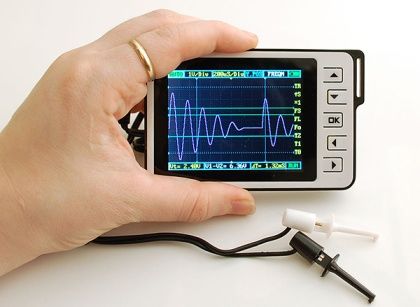

安捷伦(Agilent)的4000x系列触控萤幕示波器,包括去年发表的高阶63GHz机型以及支援13~33GHz的机种

DesignCon颁发最佳论文与最佳测试工程师奖项,得奖者开心展示讲座

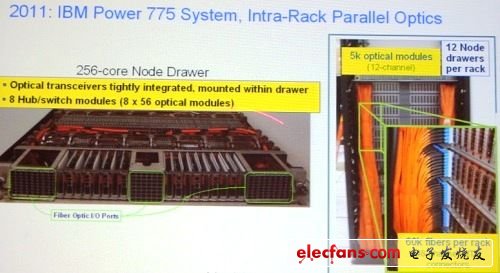

IBM工程师Christian Baks展示该公司积极开发的伺服器处理器光学互连技术的理由──他们的伺服器机架已经成为铜线丛林,很需要大扫除一番

IBM研究人员开发了两款背板原型,主处理器连结96条20Gbps光学互连;该种Holey光学互连晶片采用覆晶封装,雷射阵列透过封装上的钻孔传输资料。不过一位IBM工程师坦承,该方案非常昂贵,而且仍有些简陋;目前该公司已经正在开发40G版本

千万别愚弄工程师们──看这位DesignCon 参观者就知道,他们深知该如何仔细研究新产品

Samtec的新型FireFly连接器能支援28G铜线方案,或是今日最高速率达14G的光学互连

为了吸引参观者,NEC的工程师变装成可解决各种工程问题的超级英雄

iFixit的人员在展会现场拆解GoPro HD 摄影机等装置吸引工程师

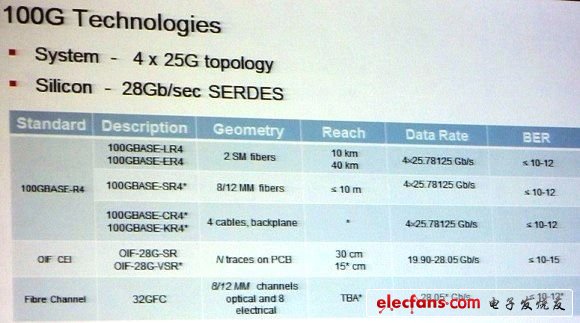

包括Google等大型资料中心业者、电信业者对新一代100G乙太网路交换器与路由器的需求,是25G讯号传输技术备受瞩目的原因;实现100G乙太网路有许多不同方案

Rambus的R+技术基本上是该公司可提升记忆体性能的IP集大成,该公司展示了透过低成本打线连结,驱动1866Mbps速率DDR3的方案;不过跟其他展示一样,该方案需要很大的外接风扇来散热

讯号完整性专家Steve Weir在现场回答参观者提问,他的标准回答模式总是「那得要根据…」;在旁边看的是英特尔的讯号完整性专家Jeff Loyer(EETTAIWAN) DesignCon大会的五大科技难题 2013年DesignCon大会日渐临近,我有五个科技难题希望得到解答。 我参加DesignCon大会的一个重要原因是为了跟上时代,芯片接口已经从5Gbits/s提升到25Gbits/s、电路板从10Gbits/s提升到100Gbits/s、系统速度向400Gbits发展。于是我的首个问题是:信号完整性领域(SI)最需要打磨的新问题是什么? 我知道这些速率,PCB的发展已经有点像无线电,怎样降低速率?我注意到组织者为这个问题准备了为期半天的培训班。

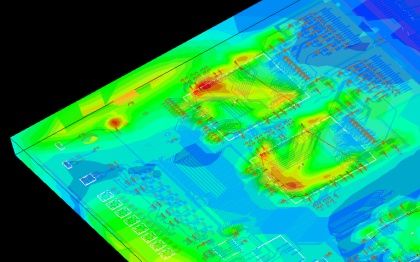

电源完整性(PI)的下一个尖端技术是? 巨型互联网技术中心为电源完整性相关讨论提供了基础。这些庞大的服务器农场必须建在发电站附近以保证供电,所以每焦耳电力都很重要。单单保证电力高效流通就已经是一门高深技艺。

测试测量公司如何保持节奏? DesignCon是我理解测试测量领域变化的必去之地。其中一个常青的分组讨论是将过去一年的问题打包进一小时讨论。今年会有来自Agilent、Lecroy和Tekrtonix的专家到场。 一位国家仪器(NI)的专题演讲演讲人会分享万米上空的测试测量应用。还有一个讨论环节会深挖细节,集中讨论PCI Express 3.0的8Gbits/s速率,包括Rohde和Schwarz在内的测试测量公司也会在一个赞助讨论环节分享千兆赫兹时代的测试。 真是太棒了,我们什么时候能有一个示波器应用?

|

网友评论